SISTEMA Y PROCEDIMIENTO PARA DETECTAR UN DEFECTO EN LAS INTERCONEXIONES DE GRAN LONGITUD DE UN CIRCUITO DIGITAL AVANZADO.

Sistema y procedimiento para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado.

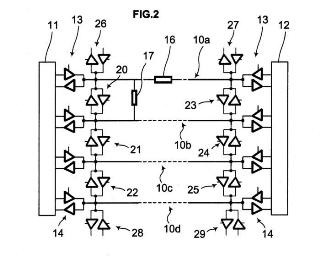

La invención se refiere a un sistema para detectar un defecto en interconexiones (10a, 10b, 10c, 10d) de gran longitud de un circuito digital avanzado, que comprende al menos un amplificador (20, 21, 22, 23, 24, 25) para disponerse entre dos interconexiones; al menos un elemento inversor; al menos un amplificador (26, 27) para disponerse entre la salida del elemento inversor y una de las interconexiones; al menos un amplificador (28, 29) para disponerse entre la otra interconexión y una de las entradas del elemento inversor; medios para deshabilitar el amplificador de excitación y el amplificador de recepción de las interconexiones; medios para habilitar los amplificadores proporcionados requeridos para generar una trayectoria cerrada a través de dichos amplificadores habilitados, las interconexiones y el elemento inversor, de modo que, en funcionamiento, se produzca una oscilación; medios para obtener la frecuencia de oscilación de las interconexiones; medios para comparar dicha frecuencia obtenida con un valor de referencia; medios para determinar la presencia de un defecto en una de las interconexiones, a partir de la comparación.

Tipo: Patente de Invención. Resumen de patente/invención. Número de Solicitud: P200900693.

Solicitante: UNIVERSITAT POLITECNICA DE CATALUNYA.

Nacionalidad solicitante: España.

Inventor/es: RIUS VÁZQUEZ,JOSEP.

Fecha de Publicación: .

Clasificación Internacional de Patentes:

- G06F11/22 FISICA. › G06 CALCULO; CONTEO. › G06F PROCESAMIENTO ELECTRICO DE DATOS DIGITALES (sistemas de computadores basados en modelos de cálculo específicos G06N). › G06F 11/00 Detección de errores; Corrección de errores; Monitorización (detección, corrección o monitorización de errores en el almacenamiento de información basado en el movimiento relativo entre el soporte de registro y el transductor G11B 20/18; monitorización, es decir, supervisión del progreso del registro o reproducción G11B 27/36; en memorias estáticas G11C 29/00). › Detección o localización de hardware defectuoso efectuando pruebas durante las operaciones de espera (standby) o durante los tiempos muertos, p. ej. pruebas de arranque.

Fragmento de la descripción:

Sistema y procedimiento para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado.

La presente invención se refiere a un procedimiento para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado que comprende dos circuitos digitales que están conectados mediante al menos dos interconexiones de gran longitud, cada una de las cuales comprende, en uno de sus extremos, al menos un amplificador para excitar la interconexión de gran longitud, y en el otro de sus extremos, al menos un amplificador para recibir la señal generada por la excitación de la interconexión de gran longitud. Más concretamente, la invención se refiere a un procedimiento para detectar circuitos abiertos y cortocircuitos resistivos en los buses de un circuito digital avanzado, tal como un circuito CMOS (por ejemplo, un microprocesador).

Además, la invención se refiere también a un sistema y a un programa de ordenador para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado, adecuados para llevar a cabo dicho procedimiento.

Antecedentes de la invención

Es conocido en el estado de la técnica que los defectos más comunes presentes en circuitos digitales avanzados (por ejemplo, circuitos CMOS) son los circuitos abiertos y los cortocircuitos resistivos.

También es ampliamente conocido el hecho de que estos defectos puede que no produzcan fallos lógicos y, por tanto, pueden permanecer indetectables cuando se aplican técnicas convencionales de verificación. De este modo, son necesarias técnicas específicas, tales como la verificación de retardo (en inglés, Delay Testing) o la verificación de IDDQ (en inglés IDDQ Testing), para detectar dichos defectos. Este hecho se describe, por ejemplo, en [J.C.M. Li, C.-W. Tseng and E.J. McCluskey, "Testing for resistive opens and stuck opens", Proceedings of ITC 2001, pp. 1049-1058], mientras que en [D. Arumí, R. Rodríguez-Montañés, J. Figueras, "Experimental Characterization of CMOS Interconnect Open Defects", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 27, No 1, pp. 123-136, January 2008] se describe el impacto del defecto en el retardo de las interconexiones.

La técnica de verificación de retardo de circuitos lógicos se basa en el hecho de que, si existe un circuito abierto o un cortocircuito resistivos, se incrementa el retardo en la interconexión y en las puertas asociadas a dicha interconexión. El principal problema es que dicho incremento en el retardo puede permanecer indetectable para las técnicas convencionales si el defecto no se encuentra en la trayectoria crítica del circuito (lo hace invisible). Una manera de detectar el defecto consiste en añadir una lógica incorporada (en inglés, built-in logic) para introducir una realimentación (es decir, feedback) en la trayectoria lógica a ser testada, de tal manera que se fuerce a que oscile. Puesto que la suma de los retardo de las puertas (y de las interconexiones) que conforman la trayectoria lógica determina el período de oscilación, éste será mayor cuando el defecto esté presente. Consecuentemente, la frecuencia de oscilación será menor. Así, comparando dicha frecuencia con un valor de referencia, es posible la detección del defecto, tal como se describe, por ejemplo, en [K. Arabi, H. Ihs, C. Duzafa and C. Kaminska, "Dynamic Digital Integrated Circuit Testing using Oscillation-Test Method", Electronic Letters, Vol 34, No. 8, pp. 762-763, April 1988], en [K. Shu-Min, Ch. Len Lee, Ch. Su and J. E. Chen, "Oscillation Ring Based Interconnect Test Scheme for SOCs", Proceedings of DAC2005, pp. 184-187] y en [H.J. Vermaak and H.G. Kerkhof, "Using the oscillation Test Method to test for Delay Faults in Embedded Cores", Proceedings of AFRICON 2004, pp. 1105-1110].

Por otro lado, la técnica de verificación de IDDQ en circuitos lógicos se basa en el hecho de que, si existe un circuito abierto o un cortocircuito resistivos, puede detectarse un consumo de energía excesivo cuando el circuito está en reposo.

De forma parecida a los circuitos lógicos, también es posible detectar fallos lógicos en las interconexiones de gran longitud (por ejemplo, buses) de un circuito digital avanzado mediante técnicas convencionales de verificación, aplicando un conjunto de patrones a la interconexión y obteniendo la respuesta a estos patrones. Sin embargo, los circuitos abiertos y los cortocircuitos resistivos pueden permanecer indetectables para estas técnicas convencionales.

En la solicitud de patente estadounidense US 6502212 B1, con título "Method and apparatus for bus parameter optimization using probes of system configurations", a nombre de Sun Microsystems, Inc. se describe un procedimiento para verificar un sistema de buses, con la intención de detectar errores en los mismos, normalmente provocados por defectos. Sin embargo, dicho procedimiento se basa en la utilización de técnicas convencionales de verificación de buses. Básicamente, el procedimiento comprende el envío de un conjunto de patrones a diferentes cadencias, tal como se ha comentado anteriormente, y se verifica que se reciben correctamente.

Descripción de la invención

A partir de lo descrito anteriormente, es un objetivo de la presente invención proporcionar un sistema para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado, siendo dichos defectos cortocircuitos o circuitos abiertos resistivos.

Este objetivo se consigue de acuerdo con la reivindicación 1, proporcionando un sistema para detectar un defecto en las interconexiones de gran longitud de un circuito digital avanzado que comprende dos circuitos digitales que están conectados mediante al menos dos interconexiones de gran longitud, cada una de las cuales comprende, en uno de sus extremos, al menos un amplificador para excitar la interconexión de gran longitud, y en el otro de sus extremos, al menos un amplificador para recibir la señal generada por la excitación de la interconexión de gran longitud, comprendiendo el sistema al menos un amplificador para disponerse, en al menos uno de los extremos de las interconexiones, entre las dos interconexiones de gran longitud, de manera que, en funcionamiento, si se habilita, conecta una interconexión con la otra interconexión; al menos un elemento inversor; al menos un amplificador para disponerse, en al menos uno de los extremos de las interconexiones, entre la salida del elemento inversor y una de las interconexiones de gran longitud; al menos un amplificador para disponerse entre la otra interconexión de gran longitud y una de las entradas del elemento inversor; medios para deshabilitar el amplificador de excitación y el amplificador de recepción de las interconexiones de gran longitud; medios para habilitar los amplificadores proporcionados requeridos para generar una trayectoria cerrada de la señal a través de dichos amplificadores habilitados, las interconexiones de gran longitud y el elemento inversor, de modo que, en funcionamiento, se produzca una oscilación; medios para obtener la frecuencia de oscilación de las interconexiones de gran longitud; medios para comparar dicha frecuencia obtenida con un valor de referencia; medios para determinar la presencia de un defecto en una de las interconexiones, a partir de la comparación entre la frecuencia obtenida y el valor de referencia.

Por consiguiente, la incorporación de la lógica adicional descrita en las interconexiones de gran longitud (por ejemplo, un bus) del circuito digital avanzado, tal como un circuito CMOS (por ejemplo, un microprocesador) permite introducir realimentación (en inglés, feedback) en las interconexiones y forzar a toda la estructura (más concretamente, los amplificadores proporcionados y las interconexiones) a que oscile. La presencia del elemento inversor genera la inversión requerida para iniciar una oscilación sostenida.

Es importante destacar que la frecuencia de oscilación depende del retardo de las interconexiones, del retardo de los amplificadores (en inglés, buffers) y del número de interconexiones y amplificadores conectados en serie. Dicha disposición en serie es la que obtiene con la presencia de los medios para habilitar los amplificadores, puesto que dichos medios son los que habilitan los amplificadores necesarios para generar la trayectoria adecuada. Además,...

Reivindicaciones:

1. Procedimiento para detectar un defecto (16, 17) en interconexiones (10a, 10b, 10c, 10d) de gran longitud de un circuito digital avanzado que comprende dos circuitos digitales (11, 12) que están conectados mediante al menos dos interconexiones de gran longitud, cada una de las cuales comprende, en uno de sus extremos, al menos un amplificador (13) para excitar la interconexión de gran longitud, y en el otro de sus extremos, al menos un amplificador (14) para recibir la señal generada por la excitación de la interconexión de gran longitud, caracterizado por el hecho de que comprende las etapas de:

2. Procedimiento según la reivindicación 1, caracterizado por el hecho de que, en la etapa (g), la frecuencia de oscilación se obtiene a partir de contar el número de oscilaciones que hacen las interconexiones de gran longitud durante un período de tiempo predeterminado.

3. Procedimiento según cualquiera de las reivindicaciones 1 ó 2, caracterizado por el hecho de que en la etapa (a) se proporciona, en cada uno de los extremos de las interconexiones, al menos un amplificador entre las dos interconexiones de gran longitud, de manera que, en funcionamiento, si se habilita, conecta una interconexión con la otra interconexión; en la etapa (b) se proporcionan dos elementos inversores; en la etapa (c) se proporciona al menos un amplificador entre la salida del primer elemento inversor y uno de los extremos de una de las interconexiones de gran longitud y al menos un amplificador entre la salida del segundo elemento inversor y el otro de los extremos de la interconexión de gran longitud; en la etapa (d) se proporciona al menos un amplificador entre uno de los extremos de la otra interconexión de gran longitud y una de las entradas del primer elemento inversor y al menos un amplificador entre el otro de los extremos de la otra interconexión de gran longitud y una de las entradas del segundo elemento inversor; en la etapa (f) se habilitan los amplificadores proporcionados requeridos para generar una primera trayectoria cerrada, en una dirección, de la señal a través de dichos amplificadores habilitados, las interconexiones de gran longitud y el primer elemento inversor, de modo que, en funcionamiento, se produzca una oscilación; en 1a etapa (g) se obtiene la frecuencia de oscilación de las interconexiones de gran longitud a partir de dicha primera trayectoria; en la etapa (h) se compara dicha frecuencia obtenida para dicha primera trayectoria con un valor de referencia; en la etapa (i), en caso de que el valor de la frecuencia obtenida sea diferente al valor de referencia, determinar la presencia de un defecto en una de las interconexiones; y por el hecho de que el procedimiento comprende además las etapas de:

4. Programa de ordenador que comprende instrucciones de programa para provocar que un sistema de computación ejecute las etapas (e) a (i) del procedimiento según la reivindicación 1.

5. Programa de ordenador según la reivindicación 4, caracterizado por el hecho de que comprende instrucciones de programa para provocar que el sistema de computación ejecute las etapas (f'), (g'), (j), (k) del procedimiento según la reivindicación 3.

6. Programa de ordenador según cualquiera de las reivindicaciones 4 ó 5, caracterizado por el hecho de que está almacenado en unos medios de grabación.

7. Programa de ordenador según cualquiera de las reivindicaciones 4 ó 5, caracterizado por el hecho de que es portado por una señal portadora.

8. Sistema para detectar un defecto en interconexiones (10a, 10b, 10c, 10d) de gran longitud de un circuito digital avanzado que comprende dos circuitos digitales (11, 12) que están conectados mediante al menos dos interconexiones de gran longitud, cada una de las cuales comprende, en uno de sus extremos, al menos un amplificador (13) para excitar la interconexión de gran longitud, y en el otro de sus extremos, al menos un amplificador (14) para recibir la señal generada por la excitación de la interconexión de gran longitud, caracterizado por el hecho de que comprende:

9. Sistema según la reivindicación 8, caracterizado por el hecho de que el elemento inversor (30, 31) comprende medios de recepción de una señal de activación.

10. Sistema según cualquiera de las reivindicaciones 8 ó 9, caracterizado por el hecho de que el defecto se seleccionada de entre los siguientes: un cortocircuito resistivo (17), un circuito abierto resistivo (16).

11. Sistema según cualquiera de las reivindicaciones 8 a 10, caracterizado por el hecho de que el elemento inversor (30, 31) es un circuito lógico.

12. Sistema según cualquiera de las reivindicaciones 8 a 10, caracterizado por el hecho de que el elemento inversor (30, 31) es una puerta lógica.

13. Sistema según cualquiera de las reivindicaciones 8 a 12, caracterizado por el hecho de que el circuito digital avanzado es un circuito CMOS.

14. Sistema según cualquiera de las reivindicaciones 8 a 13, caracterizado por el hecho de que las dos interconexiones de gran longitud son un bus.

15. Sistema según cualquiera de las reivindicaciones 8 a 14, caracterizado por el hecho de que los medios para deshabilitar el amplificador de excitación y el amplificador de recepción de las interconexiones de gran longitud, los medios para habilitar los amplificadores proporcionados requeridos para generar una trayectoria cerrada de la señal a través de dichos amplificadores habilitados, las interconexiones de gran longitud y el elemento inversor, los medios para obtener la frecuencia de oscilación de las interconexiones de gran longitud, los medios para comparar dicha frecuencia obtenida con un valor de referencia, los medios para determinar la presencia de un defecto en una de las interconexiones, a partir de la comparación entre la frecuencia obtenida y el valor de referencia, conforman un dispositivo de control del sistema.

16. Sistema según cualquiera de las reivindicaciones 8 a 15, caracterizado por el hecho de que es un sistema digital configurable.

17. Sistema según cualquiera de las reivindicaciones 8 a 15, caracterizado por el hecho de que es un controlador digital.

18. Circuito digital avanzado caracterizado por el hecho de que comprende un sistema para detectar un defecto en interconexiones de gran longitud según cualquiera de las reivindicaciones 8 a 16.

Patentes similares o relacionadas:

Vigilancia a distancia de un sistema de procesamiento de datos mediante una red de comunicaciones, del 30 de Octubre de 2018, de Accenture Global Services Limited: Un sistema de procesamiento de datos a distancia que comprende: un receptor de datos para recibir un mensaje de datos; una […]

uso de toma de huellas digitales de potencia (pfp) para monitorizar la integridad y potenciar la seguridad de sistemas informáticos, del 22 de Febrero de 2017, de VIRGINIA TECH INTELLECTUAL PROPERTIES, INC.: Método para realizar una estimación de integridad en tiempo real de ejecución de una rutina en una plataforma de procesamiento informático, que comprende: (a) […]

DISPOSITIVO DE IMPRESION, METODO DE DIAGNOSTICO PARA DISPOSITIVO DE IMPRESION Y PROGRAMA DE DIAGNOSTICO PARA DISPOSITIVO DE IMPRESION., del 1 de Junio de 2007, de SEIKO EPSON CORPORATION: Una impresora adaptada a usar una pluralidad de canales (1ch, ....8ch) para realizar la comunicación inalámbrica, que comprende; unos medios de salida […]

SISTEMA Y METODO PARA EL DIAGNOSTICO EN SERVICIO DEL SOFTWARE DE UN SISTEMA DE DISPOSITIVO DE COMUNICACIONES SIN CABLES., del 16 de Diciembre de 2006, de KYOCERA WIRELESS CORPORATION: Método para diagnóstico en servicio de software de sistema en un dispositivo de comunicaciones sin cables, cuyo método comprende: ejecutar el software del sistema […]

PRUEBA AUTOMATICA INTEGRADA JERARQUICA., del 1 de Diciembre de 2006, de INTERNATIONAL BUSINESS MACHINES CORPORATION: Un aparato para proporcionar autocomprobación integrada jerárquica para un sistema con chip, comprendiendo dicho aparato: un controlador BIST […]

PROCEDIMIENTO PARA LA VERIFICACION DE UN NUCLEO DE ORDENADOR DE UN MICROPROCESADOR O DE UN MICRO CONTROLADOR., del 1 de Noviembre de 2006, de ROBERT BOSCH GMBH: Procedimiento para la creación de una prueba automática para la verificación de la función correcta de un núcleo de ordenador de […]

APARATO Y METODO PARA RECUPERAR DATOS A DISTANCIA., del 16 de Noviembre de 2004, de ONTRACK DATA INTERNATIONAL, INC.: La invención se refiere a un aparato y a un procedimiento para recuperar a distancia datos inaccesibles sobre dispositivos informáticos de almacenamiento. El […]

DETECTOR DE CONGELACION DE IMAGEN, del 3 de Junio de 2009, de JAKOB HATTELAND DISPLAY AS: Procedimiento para identificar una situación de congelación de imagen en una pantalla, comprendiendo el procedimiento: #- añadir una firma electrónica en una señal alimentada […]

DETECTOR DE CONGELACION DE IMAGEN, del 3 de Junio de 2009, de JAKOB HATTELAND DISPLAY AS: Procedimiento para identificar una situación de congelación de imagen en una pantalla, comprendiendo el procedimiento: #- añadir una firma electrónica en una señal alimentada […]